Intel Broadwell Broadens its Horizons…In Space

Monday’s launch of a SpaceX Falcon 9 rocket carrying a Dragon spacecraft to the space station carried what will be the most powerful computer in orbit. In a joint project with HPE (HP Enterprise) NASA wants to test how high end computers, with off the shelf parts and construction perform in low Earth orbit. The computer that will be soon installed is an HP Apollo 40 series (exact model is unclear, probably PC40/SX40). It consists of 2 1U dual socket systems, running Intel Xeon E5-26xx V4 (Broadwell-EP 14nm) processors and supporting infiniband. The only modification done was to use liquid cooling vs air cooling as the EXPRESS racks on the ISS are not set up to handle the heat load the computer generates. The computers run on a standard 110VAC supply, provided by a NASA supplied inverter, which takes the 48VDC power generated by ISS’s solar arrays and converts it to the 110VAC needed by the Apollo computer.

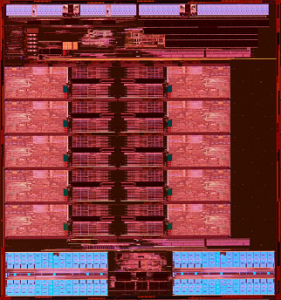

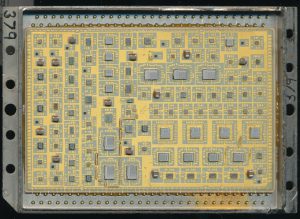

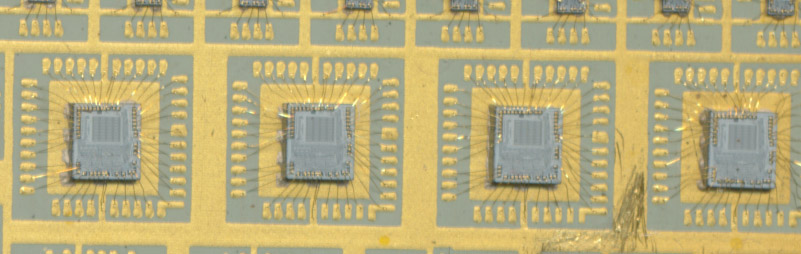

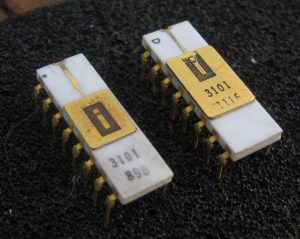

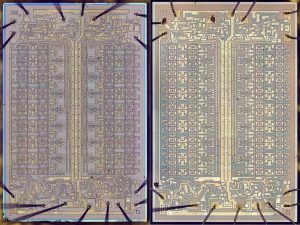

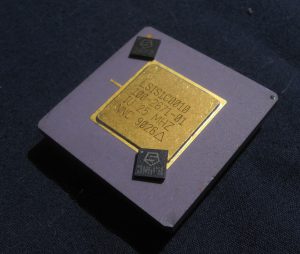

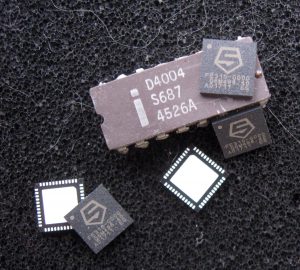

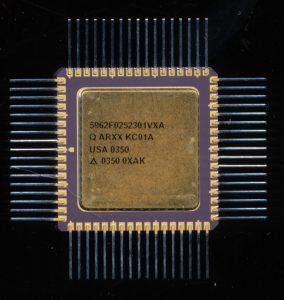

The Broadwell processors are made on a 14nm process, and are some of the latest made by Intel (NASA froze the design in March so they were the fastest available to HPE at that time). Performance will be just over 1Teraflop, a great increase over the main computers that actually RUN the ISS, which are Intel 80386SX based. The astronauts themselves use laptops of various pedigrees, mainly Lenovo Core 2 Duo based A61Ps (these are being replaced by HP Zbook 15s powered by Intel 7th Gen Core i5 and i7 processors) , so the Apollo is a great leap up from them as well.

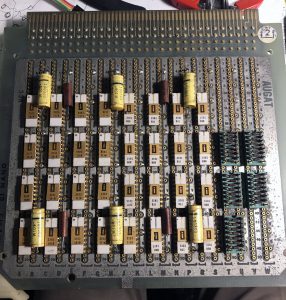

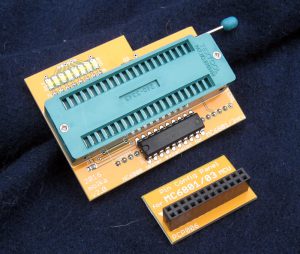

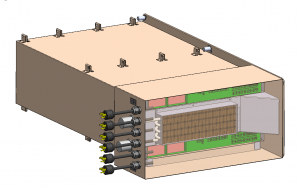

Mockup of HPE Apollo Computers for EXPRESS rack integrations. 2 computers with water cooling system between them.

To test the Apollo, NASA will run an identical system on the ground, performing the same tasks, and compare the outputs. They want to see how the computers handle the environment in space, with various loads and electrical conditions. One computer (both on the ground and on the ISS) will be run at maximum performance for the entirety of the experiment, while the other will have its computing/electrical load dynamically varied.

Radiation is usually one of the biggest concerns for space based computers, but on the ISS, radiation levels are not particularly high. Daily doses experienced by the crewmembers are in the 10-50 millirad range. There are of course periods of higher radiation, either from where the ISS is in orbit, or from space weather. The water cooling will further shield parts of the computer from radiation (water being a great radiation shield). The Broadwell-EP processors have around 7.2 billion transistors, increasing the

chance that even a small amount of radiation may have an effect. By running one set of computers at maximum performance, NASA can see these effects quickly. Does the performance decrease? Does the power draw start spiking? Or is data being lost in the Infiniband networking PCIe card?

Currently experiment data has to be transferred to the ground in raw unprocessed format, as nothing on the ISS can handle the computing need to process it. If the high performance computing experiment is successful, it can give the astronauts the ability to do processing and analysis of experimental data in orbit,. and transfer only the results to the ground, saving precious bandwidth, and allowing for experiments to be modified, changed, or created in orbit based on the ongoing results.

More Information:

NASA: HPC COTS Experiment