Chips in Space: Making MILSTAR

Back in the late 1970’s having a survivable space based strategic communications network became a priority for the US Military. Several ideas were proposed, with many lofty goals for capabilities that at the time were not technologically feasible. By 1983 the program had been narrowed to a highly survivable network of 10 satellites that could provide LDR (Low Data Rate) strategic communications in a wartime environment. The program became known as MILSTAR (Military, Strategic, Tactical and Relay) and in 1983 President Reagan declared it a National Priority, meaning it would enjoy a fair amount of freedom in funding, lots and lots of funding. RCA Astro Electronics was the prime contractor for the Milstar program, but during the development process was sold to GE Aerospace, then Martin Marietta, which became Lockheed Martin before the 3rd satellite was launched. The first satellite was suppose to be ready for launch in 1987, but changing requirements delayed that by 7 years.

The first satellite was delivered in 1993 and launched in February of 1994. A second was launched in 1995 and these became Milstar-1. A third launch failed, which would have carried a hybrid satellite that added a Medium Data Rate (MDR system). Three Block II satellites were launched in 2001-2003 which included the MDR system, bringing the constellation up to 5. This provided 24/7 coverage between the 65 degree N/S latitudes, leaving the poles uncovered.

The LDR payload was subcontracted to TRW (which became Northrup Grumman) and consisted of 192 channels capable of data rates of a blazing 75 – 2400 baud. These were designed for sending tasking orders to various strategic Air Force assets, nothing high bandwidth, even so many such orders could take several minutes to send. Each satellite also had two 60GHz cross links, used to communicate with the other Milstar sats in the constellation. The LDR (and later MDR) payloads were frequency hopping spread spectrum radio system with jam resistant technology. The later MDR system was able to detect and effectively null jamming attempts.

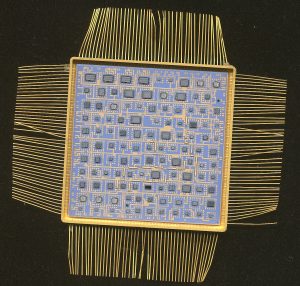

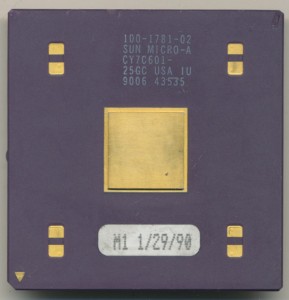

The LDR system was built out of 630 LSI circuits, most of which were contained in hybrid multi layer MCM packages. These LSIs were a mix of custom designs by TRW and off the shelf TTL parts. Most of the TTL parts were sourced from TI and were ALS family devices (Advanced Low Power Schottky), the fastest/lowest power available. TI began supplying such TTL (as bare dies for integration into MCMs) in the mid-1980’s. These dies had to be of the highest quality, and traceable to the exact slice of the

exact wafer they came from. They were supplied in trays, marked with the date, diffusion run (a serial number for the process and wafer that made them) and the slice of that wafer, then stamped with the name/ID of the TI quality control person who verified them.

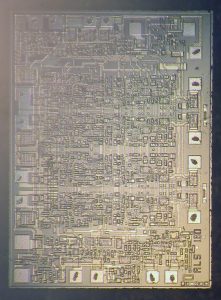

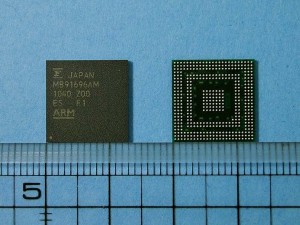

These TTL circuits are relatively simple the ones pictures are:

54ALS574A Octal D Edge Triggered Flip flop (used as a buffer usually)

54ALS193 Synchronous 4-Bit Up/Down Binary Counters With Dual Clock

54ALS161A Asynchronous 4-Bit Binary Counters

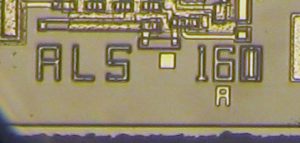

Looking at the dies of these small TTL circuits is quite interesting. The 54ALS161A marking on the die appears to be on top of the a ‘160A marking. TI didn’t make a mistake here, its just that the the 160 and 161 are essentially the same device. The 161 is a binary counter, while the 160 was configured as a decade counter. This only required one mask layer change to make it either one.

Similarly with the 54ALS574, which shares a die with the more basic ‘573 D type transparent Latch. This was pretty common with TTL (if you look at a list of the different 7400 series TTL you will notice many are very similar with but a minor change between two chips). It is of course the same with CPUs, with one die being able to be used for multiple core counts, PCI0E lanes, cache sizes etc.

Together with others they perform all the function of a high reliability communications systems, so failure was not an option. TI supplied thousands upon thousands of dies for characterization and testing. The satellites were designed for a 10 year lifetime (it was hoped by them

something better would be ready, no doubt creating another nice contract, but alas, as many things are, a follow on didn’t come along until just recently (the AEHF satellites). This left the Milstar constellation to perform a critical role well past its design life, which it did and continues to do. Even the original Milstar 1 satellite, launched in 1994 with 54ALS series TTL from the 1980s is still working, 25 years later, a testament to TRW and RCA Astro’s design. Perhaps the only thing that will limit them will be the available fuel for their on-orbit Attitude Control Systems.

While not necessarily a CPU in itself these little dies worked together to get the job down. I never could find any of the actual design, but it wouldn’t surprise me if the satellites ran AMD 2901 based systems, common at the time or a custom design based on ‘181 series 4-bit ALUs. finding bare dies is always interesting, to be able to see into whats inside a computer chip, but to find ones that were made for a very specific purpose is even more interesting. The Milstar Program cost around $22 Billion over its life time, so one must wonder how much each of these dies cost TRW, or the US Taxpayer?

Posted in:

CPU of the Day