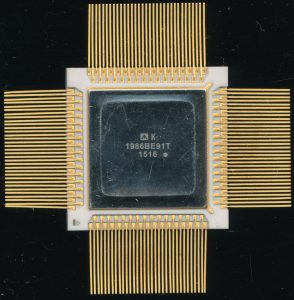

Milandr K1986VE91T – The ARM of Russia

In the early 1990’s a Milandr was formed in Zelenograd, Russia (just a short distance to the NW of Moscow), the silicon valley of Russia, home to the Angstrem, and Micron IC design houses. They are a fabless company, though with their own packaging/test facilities, specializing in high reliability metal/ceramic packages. Most of their products are fab’d in Germany, by X-Fab. X-Fab was formed in part, from the remains of the Soviet/E. German era VEB Mikroelektronik Karl Marx, in Erfurt Germany, also known as FWE/MME and later Thesys. In Soviet times it wasn’t uncommon for Soviet companies to use dies produced by FWE in their own packages, so this bit of legacy continues today.

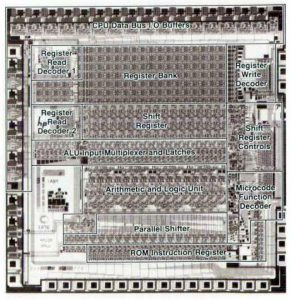

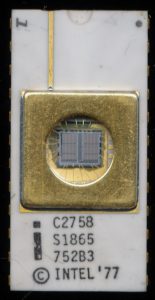

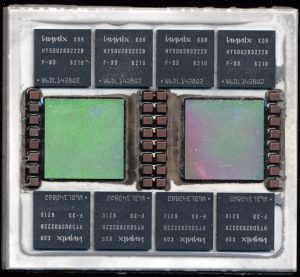

The K1986VE91T is one of Milandr’s top end products, it is an 80MHz ARM Cortex-M3 based processor, and likely one of the largest, if not the largest, Cortex-M3 made. It is made on a 180nm process and includes 32K RAM, 128K FlashROM, 96 USER I/O, USB, 2 UART and 12-bit DAC/ADC. Judging by the die, the processor was built with standard licensed blocks, very common for such designs. Milandr licensed the ARM Cortex-M3 itself in December of 2008, for use mainly in automotive and industrial applications. Milandr is also the very first Russian company to license and use an ARM core.

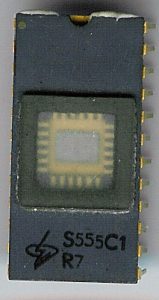

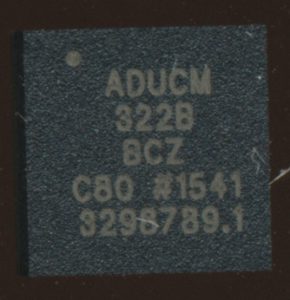

Analog Devices ADUCM322BBCZ ARM Cortex-M3 80MHz – Same basic core, but in a very much less appealing package

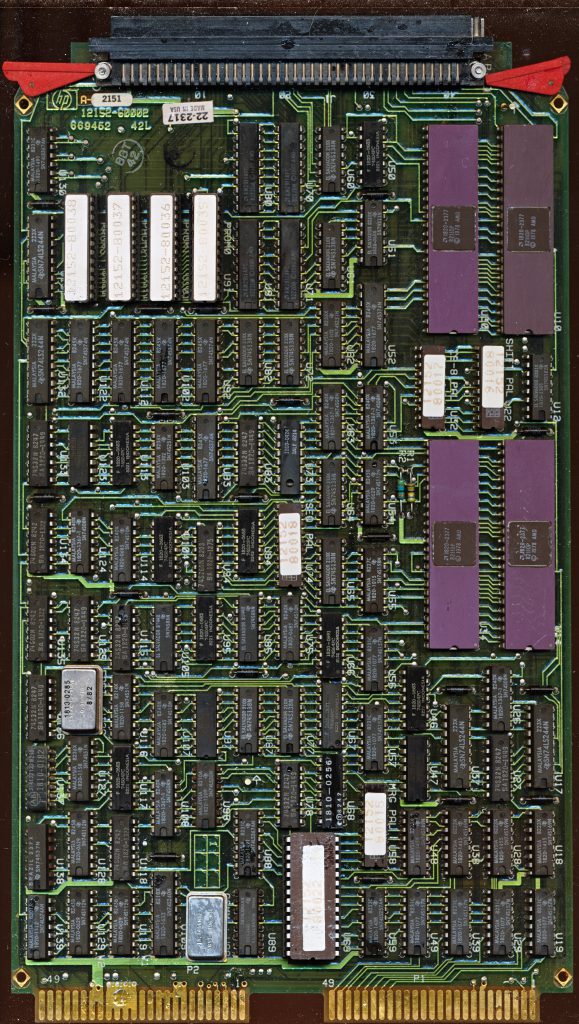

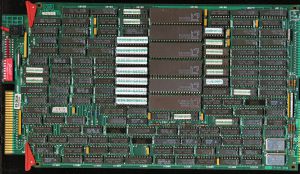

The package, however, is completely unique. It is a 132 pin CQFP package. There are 33 gold leads on each side of the white ceramic package. Each row is actually 2 staggered rows, the offset allows the finer lead pitch, and still room to bond the leads to the top of the package. Soviet processors were often delivered in the most stunning of packages and 25 years later, Milandr keeps that tradition alive.

Each of these processors came with a brief datasheet, complete with inspection stamps for the processor. It is all in Russian, but check it out here.

Milandr made several variations of the Cortex-M3, including the VE92 and VE93 which are internally identical, but with much less I/O available owing to there smaller 64 pin and 48 pin packages respectively. Milandr also made a copy of the PIC17 processor that we covered last year.

A version of the K1986VExx continues to be made by Milandr, but renamed to the MDR32F9Qx. It continues to have the same basic core, but in a 144 pin package, allowing even greater I/O support.