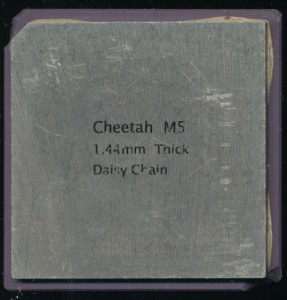

Sun UltraSPARC IIIi+ Early engineering sample from August of 2005

In early 2004 Sun Microsystems had a lot going on. The UltraSPARC IV had been announced, and Sun was already talking about its upgrade, the UltraSPARC IV+. Sun had recently released the Jalapeno, aka the UltraSPARC IIIi, their second processor with on die L2 cache (The first being the IIe designed for embedded use) in 2003. In 2002 Sun had purchased Afara Websystems for their SPARC design, known as Niagara, which became the Sun T1, and were working on its successor, the T2. Both the T1 and the UltraSPARC V (the successor to the not even itself yet released IV) was scheduled to tape out the next year, yet itself was canceled in April of 2004, most of the entire engineering staff working on it is laid off.

At the same time Sun was talking up an upgrade for the lower end UltraSPARC IIIi, this would be a relatively simple process, more the existing core to a new process. It currently was being made by TI on a 130nm 7-layer Cu interconnect process with low-k dielectric. Moving it to TI’s 90nm process would allow for greater clock speeds, less power, and room on die to quadruple the L2 cache to 4MB. The processor was code named Serrano, and widely announced as an upgrade to Sun’s Fire V215, V245 and V445 servers. Sun promised a release in late 2005. And then…

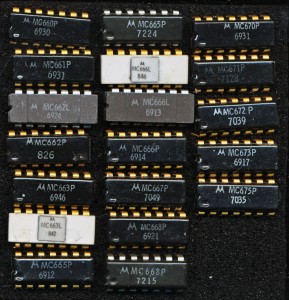

Sun UltraSPARC III Cheetah – Early Mechanical Sample. The IIIi added on die L2 cache

Nothing, talk of the Serrano went silent, all PR focus has shifted to the coming T1 and the UltraSPARC IV+. Both are released in 2005 to great applause, but the tech community is still wondering where the IIIi+ has gone? Sun isn’t exactly forthcoming as to why, mentioning that it had been delayed in order to get the T1 out the door. In mid-2006 a customer commented, “There have been problems getting the UltraSPARC IIIi+ processors, so the new systems will be released with the current chips.” Finally in August of 2006 Sun come forward and says that the IIIi+ has been canceled, but there is a catch, it was canceled the year before, and Sun decided to just keep mum about it.

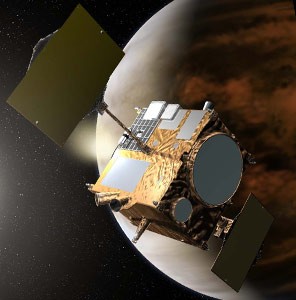

Keep in mind the IIIi+, other then the increase in L2 cache, was a fairly ‘routine’ port to a new process. The delays, and cancellation at the time sounded like it was due to technical grounds, but looking back, and seeing that they had working silicon in 2005, it would seem that the decision to kill the Serrano was resource driven. Likely a combination of Sun’s engineering and marketing constraints, as well as the availability of the 90nm process at TI, which was also being used for the Niagara.

Manufacturing capacity is a finite resource, so not using up what may have been a very limited amount of fab space, on a processor that was designed to slot into the low end servers, is possibly the best explanation we have for the cancelling of the UltraSPARC IIIi+, perhaps a former Sun engineer can fill in some more details, as so many of them were laid off whom had worked on Sun’s previous processors. It was a gamble by Sun, and one which seems to have paid off, considering the success of the Niagara, though Sun/Oracle were far from done with canceling designs, Honeybee, Rock, and M4 all come to mind.