The RCA Solid State Technology Center (SSTC)

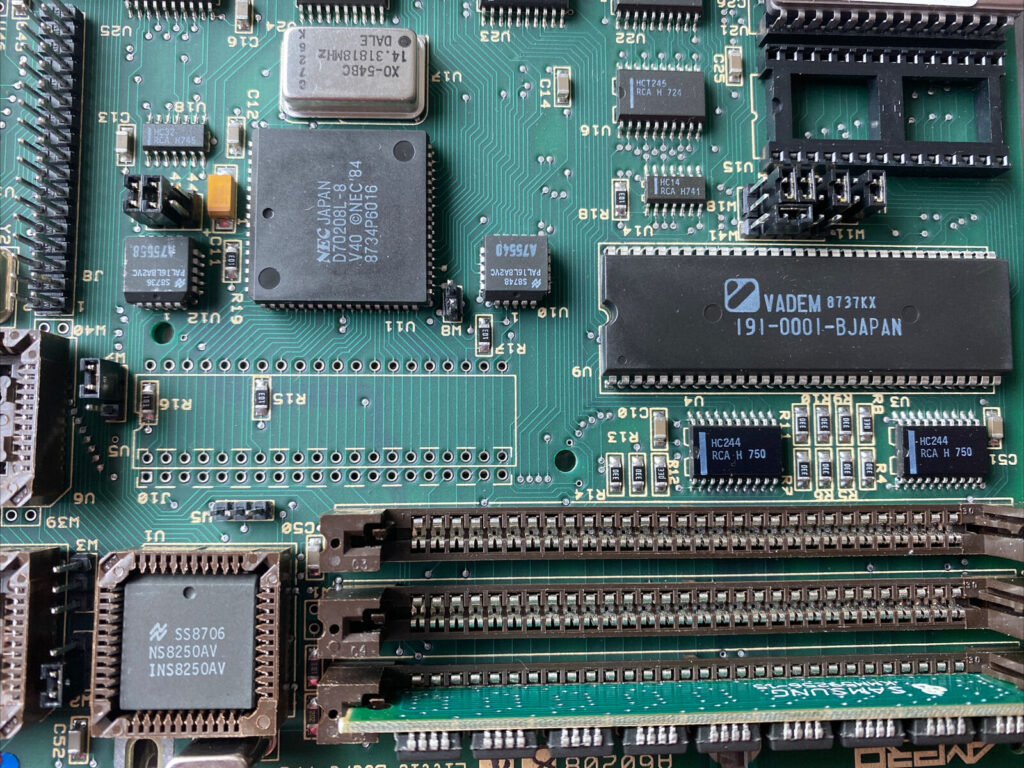

Today most chips we use are made in CMOS (Complimentary Symmetrical Metal Oxide Semiconductor), which is a process using both p-type and n-type MOSFET transistors. It was invented back in 1963 by Fairchild, but was commercialized by RCA in 1968 with the introduction of the CMOS based 4000 series of MSI logic devices. These were basic IC’s with such things as NOR gates, Adders, Flip flops and the like. A CMOS equivalent to TI’s popular TTL based 7400 series.

RCA also made a series of computers in the 1960’s (to compete with IBM) as well as other electronic products. including many for the US Air Force, NASA and US Army. In 1970 RCA created the SSTC (Solid State Technology Division) in Somerville, New Jersey to develop CMOS processes (and Silicon on Sapphire versions) into more commercial products. At the time most IC’s (outside the 4000 series) were made in PMOS or NMOS, CMOS was considered too slow, despite is lower static power usage and high noise immunity. SSTC was to develop processes, standard, and eventually devices, that RCA could then commercialize and/or use in their other products (such as their computer line, radios, and military products). It was out of this project that the famous COSMAC processors (CDP1801 and CDP1802 line) came from.

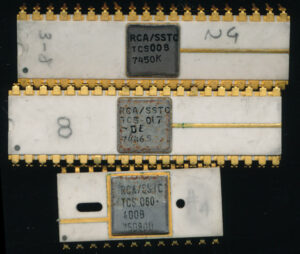

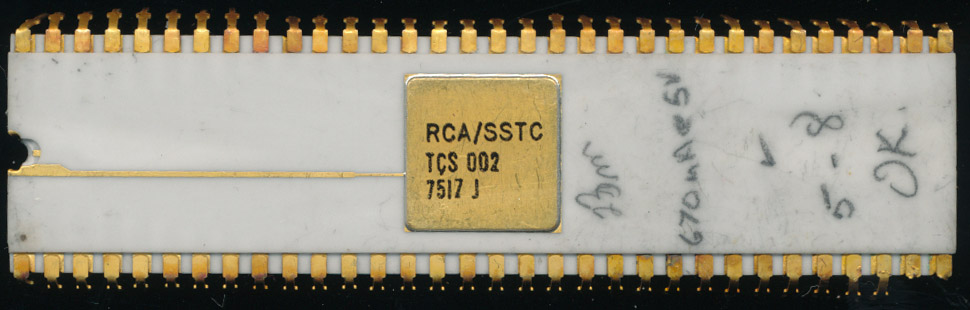

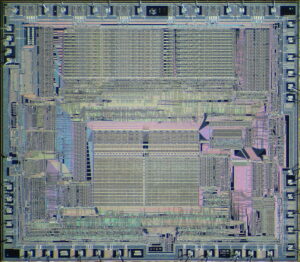

SSTC also made a series of essentially standard test devices. These were based on a common cell architecture (more common in ASICs today) with a series of chips made to demo what was possible with the CMOS-SOS (CMOS on Sapphire) process. These ‘standard’ IC’s would then be used in various demo products for potential customers. The most interested customers at the time were the US Air Force and NASA. The RCA CMOS process allowed for a great power savings, and especially when built on a sapphire substrate, exhibited a high tolerance to radiation, useful for the then rapidly expanding satellite/space market.

The first of these chips were made in 1974-1975 and were made with a 7 mil (178micron) standard cell height, on a 20 micron process. Versions were also made with a 5 mil (127 micron) size, specifically for the military market. These were not typically commercially available devices, but used internally for test, evaluation, and to build specific products, though the technology used for them was often turned into generic products.

Below is a list of some of these devices SSTC made. The TCS prefix was used to denote these being made by SSC on a CMOS-SOS process. A TCC prefix is a standard CMOS process.

| Device | Function |

| TCS001 | 16×16 Multiplier |

| TCS002 | 16×16 Multiplier 200nsec |

| TCS008 | 8×8 Adder |

| TCS015 | 18-bit Reclocking Register with complement select |

| TCS016 | Dual 8 -Bit Position Scaler for Floating Point Applications and Other Binary Division. |

| TCS017 | Floating Point Control for FFT Arithmetic Unit of Arbitrary Radix (Parallelism) |

| TCS026 | Floating Point 2×1 Multiplexer – 163 gates** |

| TCS027 | 12-bit Up/down counter (8+4) – 300 gates** |

| TCS029 | Unknown** |

| TCS030 | 8-bit Adder = 450 gates** |

| TCS031 | 9-bit 4×2 Multiplexer – 150 gates** |

| TCS032 | Adder Multiplexer Control – 166 gates** |

| TCS039 | Multiplier |

| TCS040 | Correlator |

| TCS043 | D/A converter (rad hard) |

| TCS045 | Code Generator |

| TCS047 | Frequency synthesizer |

| TCS057 | 9×9 Multiplier (8×8 + sign) |

| TCS060 | Shift Register with Variable Length, Complementing Functions and Switched Delays. Total Registers = 38 Bits |

| TCS065 | 9+9 Adder(8+8 + sign) |

| TCS074 | ROM |

| TCS130 | 16K SRAM |

| TCS151 | 4K SRAM |

**Used to build the NASA 32-bit SUMC (Space Ultrareliable Modular Computer)

These were used in many military products such as the AN/GVS-5 handheld laser rangefinder, a Programmable waveform generator used in FM RADARs, and for the imaging system (digitization and compression of video to be sent) in the remotely piloted Lockheed MQM-105 Aquila drone (yah drones, back in 1975). The Aquila project was particularly challenging, as the circuitry had to be small enough, and low power enough to fit on a small airframe, yet still handle video compression fast enough that a ground station could receive and decode useful imagery. This was done with several large hybrid circuit modules consisting of many TCS057 Multipliers and TCS065 Adders. This was capable of 200-1600Kbps data rates, not bad in 1975.

Most of the TCS line of components was capable of 10MHz operation while running at 5V, and voltage and clock rate scaled with each other, so they could be clocked lower for less voltage and power usage, or clocked higher at the expense of more power.

It is a bit unfortunately that RCA lost its way in the 1970’s, attempting to became a conglomerate, they became known as Rugs, Chickens and Automobiles (having bought parts of Hertz Rental Cars, a frozen TV dinner company, a carpet company and others). They were bought by GE in the 1980’s and in 1988 the Solid State Division, with what remained of the SSTC was purchased by Harris Corporation, which continued to make the 180x line of CMOS processors for over 20 years. If RCA had stayed focused on making CMOS a commercial success, we may have had more and faster CMOS processors nearly a decade sooner.

Posted in:

CPU of the Day