CPU of the Day: National Elentari x86 and What Lies Beyond – Part 2

Last week we talked about a little known, but not unheard of 486 built by National Semiconductor called the NS486 Elentari. As interesting as a non-Intel x86 architecture is, thats not what led me down the aforementioned rabbit hole. This is what did…

This small blurb in Boot magazine from back in August of 1997 is all it took. What was this mysterious N7 processor that even Boot Magazine felt the need to mention? It is being compared to the Cyrix MediaGX, which coincidently National had agreed to merge with right about the time this issue went to press, a fact that may or may not have been known to the authors at the time. Regardless, the deal wasn’t officially completed until 1998, so that meant this mysterious N7 had been in development for some time, and probably had reached something a bit more then a glitter in an engineers eyes….and indeed it had.

Mentions of the ‘N7’ in the press at the time start in early 1996 and continue through 1997, this indicates that the N7 was likely planned soon after the beginnings of the NS486 core. Its very likely that the NS486 was to be a stepping stone to the bigger more powerful N7. The N7 is described as a 133MHz ‘Pentium compatible’ processor. The NS586 core (as it was called by National) was an enhanced NS486, with the pipeline extended to 5-stages and using Nationals new 0.35u process, just as some had originally suggested for the NS486. This resulted in a 3.3V processor running at 133MHz.

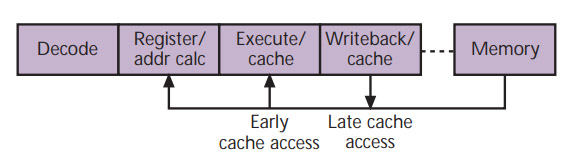

NS586 5-Stage Pipeline – Cache could happen on Stage 3 or 4 and Memory Access was non-blocking (image (c) MPR)

The NS586 was planned to be at least 2, and most likely 3 different processors (in similar fashion to the NS486SXF and NS486SXL). The common core to all of the designs was the 5-stage NS586. This took the NS486 and greatly enhanced it, adding 8 of L1 cache (4K Instruction + 4K Data). The pre-fetch buffer is doubled in size to 32-bytes as well as some Out of Order execution support. The decode and memory/cache access logic is also further optimized. Cache accesses can be shifted between the 3rf and 4th stages as needed, allowing modifying, loading or storing of cache data in two consecutive cycles. Unlike the K6 or PII the NS586 does not use intermediate instructions in executing x86 code, it directly executes each x86 instruction (like the NS486 before it). The updated pipeline executes all code as fast or faster then a 486 and in some cases faster then a Pentium. National claimed that the 133MHz core would perform as a Pentium 95, compared to say a AMD 5×86-133 being rated at a Pentium 75 level. As with the NS486 before it, it lacked an onchip FPU.

The NS586 core was not exactly small, even on the 0.35u process it took 930,000 transistors (426,000 of which is the cache). This resulted in a die size of around 25.8mm2. (roughly the same size as the core only NS486 on 0.65u). And it was intended to be even bigger…

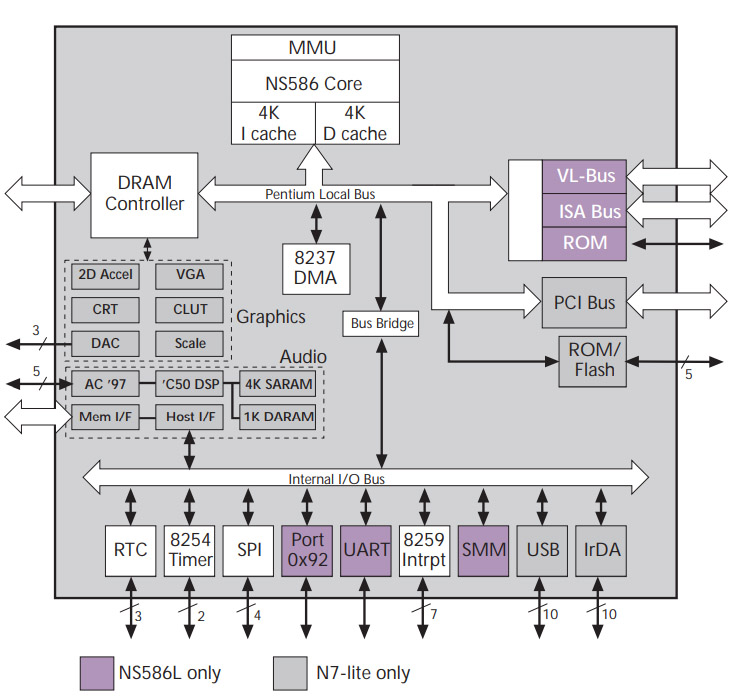

Lise the NS486 before it, the NS586 was to be integrated with a variety of peripherals, and this time National was going big on the integration. At the top was the N7-Lite, which integrated the NS586 core with a SVGA 2D graphics controller, TI TMS320C50 based DSP and Audio controller. This in addition to a PCI bus, DMA controller USB, IrDA, and other normal peripherals of the era. The N7-Lite does not have a traditional DRAM controller, instead using a controller geared towards a UMA (Unified Memory Architecture) to use the system RAM for the CPU and the onboard GPU. The GPU is designed to support only a TV out (NTSC PAL and SECAM outputs) as this was to be a full NetworkPC on a chip, basically what became Set-Top Boxes of the 1990’s.

NS586L and N7-Lite shared the same core but with different peripherals as well as busses (image (c) MPR)

On the low end was the NS586L, which dropped the audio, video, and PCI bus and added a standard Pentium compatible VL-Bus, ISA, and DRAM/ROM controller, this is more of a enhanced NS486 with a similar set of peripherals, and likely would be the logical successor to designs using the 486. Speed was to be 100MHz (again to differentiate it from the N7-Lite) and estimated cost was to be $25/chip. Pricing for the N7-Lite was not announced. It’s unknown how far these designs progressed, whether actual silicon was made or not. Having a transistors count and die size was indication they were pretty far along, perhaps having the chips floor plan finalized and working on taping it out for masks (6 months seems reasonable for samples after tape out).

Both of these chips were scheduled (as of October of 1997) to begin sampling in the second quarter of 1998. Its very likely that a third chip was planned, if only due to the naming of the ‘N7-Lite.’ ‘Lite’ indicates that it is something less then the full version, and the Boot blurb (as well as some other press mentions) only refers to the ‘N7.’ In all likelihood there was to be a top end version known simply as the N7. Such a chip would likely replace the TV only GPU in the N7-Lite with something that supports standard CRTs or LCD panels, perhaps more RAM support and Ethernet and/or an EIDE hard drive controller (something that the competing Cyrix derived ST STPC included). We may never know, as despite the efforts of the engineering team the project was inevitably canceled in favor of the newly acquired MediaGX line from Cyrix. This line continued to be developed at National even after they sold the rest of Cyrix off to VIA (eventually selling the MediaGX division to AMD).

Perhaps someone who worked in the Arador group at National can offer more insight, but until then we can only speculate of what could have been another interesting processor on the x86 scene in the 1990’s.