CPU of the Week: Intergraph Clipper C4 MCM

Fairchild developed the Clipper architecture in 1986, and sold it to Intergraph in 1987. The design never enjoyed wide success and was only used in systems made by Integraph, as well as some by ‘High Level Hardware.’ The deign itself was RISC like and competed mainly with the Sun SPARC processors.

The final version was the C400 which was released in 1993 (preceded by the C100 and C300). Presumably there was a C200 but I have not seen any documentation on it. The C400 ran at 50MHz (like the C300) and actually consisted of 3 separate chips. The CPU, the FPU and the CAMMU (Cache/Memory Management Unit). Intergraph developed their own version of UNIX called CLIX to run on the clipper, and demonstrated a version of Windows NT that ran on the C400 as well. Ultimately the lack of software support, and the slow adoption killed the Clipper. While Intergraph was designing the C5, Intel assured them a good supply of processors, and this convinced Intergraph to cancel the C5.

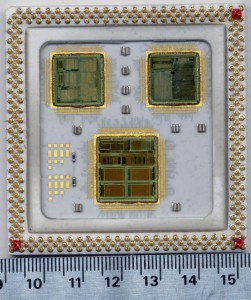

It was also available as a MCM (multi-chip-module) incorporating all three dies in a single ceramic package. This is one of the nicest looking MCMs I have seen, unfortunately the bottom plate was missing when I got it, but the dies are at least visible. I unfortunately am not sure which die is which so if you know, let me know.

February 28th, 2013 at 8:41 pm

The large chip at the bottom is most likely the CAMMU–not only because of its size (being largely SRAM and fusing off a block/TLB entry being practical, yield could be better) but also having four large regular blocks (each C100 CAMMU had two such blocks and there were separate I and D CAMMUs). The top right chip looks very similar to the FPU section in the C100 (Figure 7, pdf page 23, “The Fairchild CLIPPER: Instruction Set Architecture and Processor Implementation”) and the relative complexity of the top left chip seems to match much better the instruction and integer processing portions of the C100 (same die image/floorplan source).

February 28th, 2013 at 8:51 pm

Thank you for the info, that does make sense.

-John

February 28th, 2013 at 11:17 pm

The image here (http://www.cpu-collection.de/showimage.php?i=Intergraph_Clipper-C4_card&s=big&tb=1&r=0 ) confirms that the bigger chip is the CAMMU and if the shown surface of your image would be the hidden surface of that image–logic/’pins’ close to the board–then my identification of the FPU would be correct (assuming a board layout with the chips would be the same as a MCM layout), otherwise the CPU and FPU are reversed.

November 4th, 2014 at 10:36 am

I can’t remember who on out team designed this, but I do remember seeing the design in our MCM Engineer product. At the time we did allot of fabrication Coors Ceramics.

November 4th, 2014 at 10:38 am

So this is the slower C4, as we had one running at 100mhz with a cooling port in the ceramic, in the middle.

July 19th, 2018 at 11:57 am

I worked for Intergraph’s Advanced Processor Division (APD) in Palo Alto, CA for a couple of years. I was hired to work on the simulation and verification of an ECL version of a Clipper CPU powered computer implemented in Fujitsu ECL gate arrays (a whole bunch of them). The power consumption was off-the-charts and required liquid cooling. A large radiator was used that had to be mounted under the floor in order to duct the heat away. There was a large 10 Kilowatt (I believe) power supply.

The cooling required several gallons of Fluorinert which was pumped in between the boards and over the chips, then through the radiator which had two 12″ fans. This is very unlike the liquid cooling used these days in high powered PCs because the chips and boards were actually bathed in the coolant itself. The boards were mounted inside a large Plexiglas case for show.

The advancement of CMOS CPUs was rapidly catching and eventually surpassing the 300 MHz (if my memory serves me correctly) clock frequency of the ECL behemoth. The project was cancelled because of this.

My facts and figures may be incorrect because this was all happening in the 1989/1990 time frame.

July 19th, 2018 at 12:25 pm

Very interesting, and a very similar cooling regime as some of the Cray supercomputers used (also using ECL cooled by Fluorinert)

March 9th, 2019 at 5:31 am

BTW I was looking at doing an SBC with the Clipper C300 (IIRC, I don’t think it was the C400, I still have all the technical info somewhere) but the 486 came out just then and that was that for Risc chips in a lot of areas (also O/S hassles didn’t help, more so as the 486 caused Risc versions of NT to disappear). I still have some A0 step 486s and they also needed a lot of cooling – too much to ship a product, due to chip issues that were fixed in the next versions; also not all the instruction set executed incorrectly, you could boot DOS but a Dir listing would look a bit screwy.