SiFive FE310: Setting The RISC Free

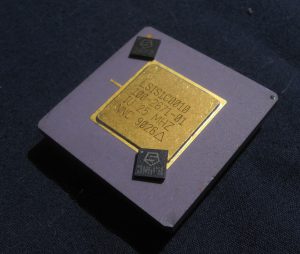

SiFive FE310 RISC-V Processor. Early LSI SPARC Processor for size comparison. Both are based on U.C. Berkeley RISC designs.

The idea of RISC (Reduced Instruction Set Computer) processors began in education, specifically University of California, Berkeley in the early 1980’s, and it was out universities that some of the most famous RISC designs came. MIPS, still in use today, started life as a project at Stanford University, and SPARC, made famous by Sun, and now made by Oracle and Fujitsu, started life as a Berkeley University project. Universities have continued to work with RISC architectures, for research and teaching. The simplicity of RISC makes them an ideal educational tool for learning how computers/processors function at their basic levels.

By the late 1980’s RISC had begun to become a commercial revolution, with nearly every player having their own RISC design. AMD (29k), Intel (i960), HP (PA-RISC), Weitek (XL8000), MIPS, SPARC, ARM, Hitachi (SH-RISC), IBM (POWER), and others offered their take on the RISC design. Most were proprietary, while a few were licenseable, none were open architectures for anyone to use.

Unfortunately, outside of the university, RISC processors are not as simple. The architectures, and their use may be, but licensing them for the design is not. It can often take more time and effort to license a modern RISC processor then it does to actually implement it. The costs to use these architectures,both in time and money often prohibit their very use.

SiFive FE310 – Sample Donated by SiFive. Full 32-bit RISC on a 7.2mm2 die in a ~36mm2 package

It is out of this that SiFive began. SiFive was founded by the creators of the first commercially successful open RISC architecture, known as RISC-V. RISC-V was developed at Berkeley, fittingly, in 2010 and was designed to be a truly useful, general purpose RISC processor, easy to design with, easy to code for, and with enough features to be commercially useful, not limited to the classroom. It is called the RISC-V because it is the fifth RISC design developed at Berkeley, RISC I and RISC II being designed in 1981, followed by SOAR (Smalltalk On A RISC) in 1984 and SPUR (Symbolic Processing Using RISC) in 1988. RISC-V has already proved to be a success, it is licensed freely, and in a way (BSD license) that allows products that use it to be either open, or proprietary. One of the more well known users is Nvidia, which announced they are replacing their own proprietary FALCON processors (used in their GPUs and Tegra processors) with RISC-V. Samsung, Qualcomm, and others are already using RISC-V. These cores are often so deeply embedded that their existence goes without mention, but they are there, working in the background to make whatever tech needs to work, work.

The RISC-V architecture supports 122 instructions, 98 of which are common to almost all prior RISC designs and 18 common to a few. Six completely new instructions were added to handle unique attributes of the architecture (using a 64-bit Performance Register in a 32-bit arch.) and to support a more powerful sign-injection instruction (which can be used for absolute value, among other things). It uses 31 32-bit registers (Register 0 is reserved for holding the constant ‘0’) with optional support for 32 floating point registers. True to the RISC design, it is a pure Load/Store processor, the only accesses to memory are via the Load/Store instructions.

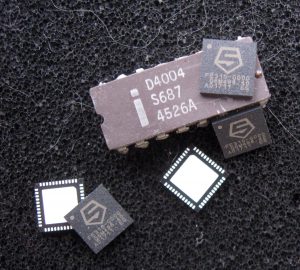

Intel 4004 with 5 SiFive RISC Processors. The 4004 was meant for a calculator. The FE310 is meant for whatever your mind may dream up.

SiFive is unique among RISC IP companies. They not only license IP but also sell processors and dev boards. The FE310 (Freedom Everywhere 310) is a 320MHz RISC-V architecture with 16K of I-cache and 16K of scratchpad RAM fabbed by TSMC on a 180nm process. Even on this process, which is now a commodity process, the FE310’s efficient design results in a die size of only 2.65mm x 2.72mm. On a standard 200mm wafer , this results in 3500 die per wafer, greatly helping lower the cost. Its an impressive chip, and one that is completely open source. What is more impressive is licensing SiFive cores, it is a simple and straightforward process. The core (32 bit E31 or 64-bit E51) can be configured on SiFive’s site, with pricing shown as you go. The license is a simple 7 page document that can be signed and submitted online. Pricing starts at $275,000 and is a one time fee, there are no continuing royalty payments. The entire process can be completed in a week or less.

In comparison, ARM, the biggest licensor of RISC processors, does not publish pricing, charges 1-2% royalties on every chip made, and has a license process that can take over a year. The base fees start at around $1 million and go into the 10’s of millions, depending on how you want to use the IP, where it will be, and for how long. For many small companies and users this is simply not feasible, and it is these smaller users that SiFive wishes to work with. Licensing a processor for the next great tech, should not be the hurdle that it has become. Many great ideas never make it to fruition due to these roadblocks. We look forward to finding SiFive processors and cores in all sorts of products in the future.

Thanks to SiFive for their generous donation of several FE310 processors to the CPU Shack Museum.