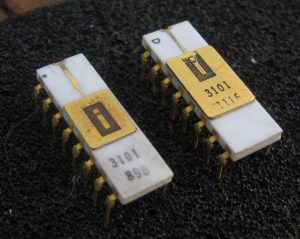

Intel’s First: The 3101 64-bit Bipolar Memory

Today when we think of Intel, the ‘processor company’ comes to mind. It was now what they are best known for, but when Intel began in 1969 they did not make processors, they made memory, specifically SRAM, DRAM, and EPROMs. The very first product Intel released, in April of 1969, was the 3101 64-bit SRAM. It was made on the new, and fast Schottky Bipolar process. This made it very fast (access times of 60ns) but very power hungry. It dissipated 525mW, over half a watt, for 64-bits of memory.

Two months later Intel released the 1101, which was developed at the same time as the 3101. It was made on a PMOS process, which allows much greater densities, the 1101 was 256-bit SRAM chip. The sacrifice is speed, the 1101 is a bit slow, with access times of around 1.5us. Operating power was 700mW but in standby mode it only drew 350mW.

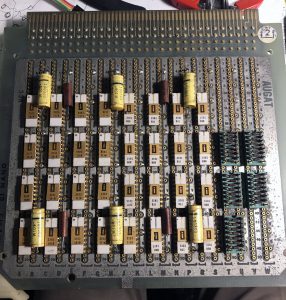

Very Early Burroughs “D” NanoMemory board with 32 Intel 3101 memories (picture from Evan Wasserman )

Computer makers were eager for single chip memories, they allowed for more dense memory systems. One of the first users of the 3101 was Burroughs in their ‘D’ machine, a computer designed for the Air Force in 1969. It used 3101s for its ‘nanomemory’ organized as 64×56 bits (needing 56 3101s if they were used for all the nanomemory. Other notable users was in implementing the stack in the Datapoint 2200. The 2200 is the grandfather of x86, its architecture was the basis for the Intel i8008, which then led to the 8080 and 8086 processors. The first Xerox Alto’s also used the Intel 3101, arguably the first GUI implementation.

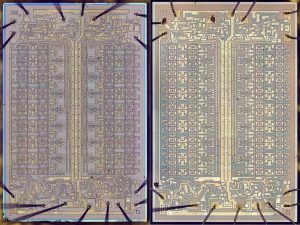

The 3101 evolved as Intel learned the process of making chips, and assembling them. This is notable in looking at die shots of two 3101s with lot codes likely only a few months apart. Ken Shirriff, a fellow collector, was donated a pair of 3101s nearly identical to those pictured, for decapping and die shots, by Evan Wasserman (who donated several to the CPU Shack Museum as well). If addition to the package difference (not the larger lid on the later one) there is some die changes as well. The bonding pads were made much larger, likely to ease the assembly, and the main VCC line on the top of the die was made smaller. Connections to bond pads were also cleaned up and refined. The logic of the device appears unchanged.

3101 dies. Left is lot 898, right is the later 1116. Click for much larger version. Die photos provided by Ken Shirriff

Through the 1970’s and well into the 1980’s memory devices were by far Intel’s largest revenue source. It wasn’t until fierce competition in the memory market that this changed. Had it not been for IBM adopting x86, things could have been much different and more difficult for Intel. The rapid adoption of x86 gave Intel a new revenue stream, and one that was less likely to be pressured by commodification as was happening to memory devices.

Posted in:

CPU of the Day