TI TMS9900/SBP9900: Accidental Success

In June 1976 TI released the TMS9900 16-bit processor. This was one of the very first 16-bit single chip processor designs, though it took a while to catch on. This is no fault of its own, but rather TI’s failure to market it as such. The 9900 is a single chip implementation of the TI 990 series mini-computers. It was meant to be a low end product and thus was not particularly well supported by TI, who did not want to cut into the higher margins of their mini-computer line. By the late 1970’s TI began to see the possibilities of the 9900 as a general purpose processor and began supporting it with development systems, support chips, and better documentation. If TI had marketed and supported the 9900 from its release the microprocessor market very much may have turned out a bit different. A large portion of Intel’s success (with the 808x) was not due to a good design, but rather good support and availability.

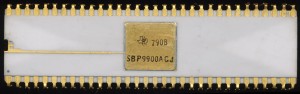

The original TMS9900 was a 3100 gate (approx 8000 transistors) NMOS design running at up to 3MHz. It required a 4-phase clock and 3 power supplies (5V, 12V, -5V). It had a very orthogonal instruction set that was very memory focused, making it rather easy to program. General purpose registers were stored off chip, with only a PC, Workspace Register (which pointed to wherever the general registers would be) and a Status Register on chip. This made context switching fairly quick and easy. A context switch required saving only 2-3 registers. The 9900 was packaged in a, then uncommon, and expensive, 64 pin DIP. This allowed the full 15-bits of address and 16-bits of data bus to be available.

TI had a trick up their sleeve for the 9900 line…

Due to TI’s experience and capabilities in other products they were able to do something with the 9900 that other companies were less capable, or willing, to do. The TMS9900 was NMOS, which for general applications was fine, but at the time was not ideal for applications that needed better reliability and ruggedness. Shortly after releasing the NMOS version TI released a bipolar I2L version. Bipolar injection logic is current driven, rather than voltage, this gives it much great noise immunity and stability. It also allows the processor clock to be scaled with current, down to a static clock. The I2L version was called the SBP9900. It contained 6034 gates and was made on a 4.5 micron process. Speed was initially 2.6MHz max at 500mA of current. The SBP9900A increased this to 3MHz max at approximately the same current. Current (and clock) could of course be reduced as needed for lower power environments. The SBP9900 was used extensively in military designs due to its inherent ruggedness. Versions were made for military temperature range as well as fully qualified MIL-STD-883 devices.

The TMS9900 eventually found wider use in data processing environments as well as the TI-99/4 home computer, which was sold in the early 1980’s. TI licensed the design to AMI and SMC to increase its availability as well released a 4MHz capable part to help relieve the speed bottleneck.

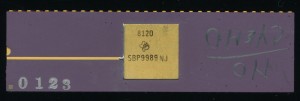

In 1980 TI released the SBP9989, a greatly enhanced 9900. It ran at up to 4.4MHz and contained 4788 gates. It was still made on a 4.5 micron bipolar process, the speed improvements coming from an improved design. It added larger memory addressing and 4 new instructions, among other things. A 0.5x process shrink to 2.25 micron was planned for the SBP9989E (later renamed the 9990) though it does not appear any of these made it to production.

TI also made several derivatives of the TMS9900. The 9980 was a 40 pin DIP version with an 8-bit data bus and 14 bit address bus operating at 2.5MHz. The 9980 continued to use 3 power supplies, while the later 9981 reduced this to 2 (5V and 12V). The main advantage of the 9980 was the reduced pin count and thus reduced cost. In 1978 a 9980 cost $30 while a TMS9900 cost $70. (an SBP9900 was MUCH more, at $193-$425 per chip, depending on the rating). A microcontroller version was also made, with on 2K ROM and 128 byes of RAM (typically used as the register set), called the TMS9940. The 9940 was the first NMOS 9900 to require only a single voltage (5V). It ran at 3MHz and was packaged in a 40 pin DIP.

The 2nd generation of the 9900 was released in 1982 and called the 9995, which required only a 5V supply and ran at 12MHz. Later versions (the TI 99105, 110 and 120) ran on a 24MHz external clock, divided by 4 internally for a 6MHz clock. TI continued to emphasise the memory speed/efficiency of the 9995 and 991xx rather then its raw clock speed.

The TMS9900 continued to see use into the mid-1990’s, typically in telecoms and other dataprocessing tasks. Like many processor designs, the 9900 didn’t die, it provided the basis of TI’s current 16-bit MCU line, the MSP430 series. The MSP430s instruction set is heavily influenced by the 9900 and largely retains its memory architecture and orthogonal instructions.

February 5th, 2015 at 5:03 pm

The TMS9900 also found a home in TI’s PLC (Programmable Logic Controller) line, the PM510, 520 and 550. These PLC’s were very popular in the process control and petrochemical markets, with the PM550 having built in PID algorithms that were uncommon at the time. At one meeting on the design of their next PLC, the 560, management asked engineering ‘How do we compete against Allen Bradley?’ One of the lead engineers responded ‘Don’t force us to use TI processors.’ And it was so. The 560 was 68000 based.

February 13th, 2015 at 1:02 am

[…] TI TMS9900/SBP9900: Accidental Success […]

May 20th, 2015 at 12:58 am

[…] into the market with one of the first microcomputers, the 4-bit TMS1000, and the top of the line TMS9900 16-bit processor, TI saw the need to fill in the middle, the 8-bit market. TI didn’t want […]

June 22nd, 2017 at 9:18 pm

Back in 1977, the TMS 9900 was ahead of it’s time when the 8-bit 8080 and 6502 microcomputers dominate because of their lower price. The 9900 architecture had a linear memory map (unlike Intel’s segmented memory processors), MMI/O interface, and a “workspace pointer” register to quickly hardware context switch it’s set of registers that reside in memory. Unfortunately the TI/99 sold to consumers did not take advantage of the 16-bit design and made it into a cheap 8-bit computer.

The rad-harden SBP version of the the 9900 series was used on the first 2 blocks of the GPS satellites and P-80 satellite.

April 1st, 2018 at 12:58 am

The “PM510” Randy dawson mentions was the TI-510 it used a Rockwell sy6502 processor. I know because I was one of the original Factory Service Techs and wrote a troubleshoot program we used with Fluke 9010A microprocessor troubleshooter in the Factory Service Center. I also repaired the PM550, TI 520, TI 530, and the more advanced versions of the 530 that were on a single board that used the 9995 and 99105. The PM-550 used the Motorola 68000, the 575 and a version of the boards manufactured for a robotics controller, made for a company called COMAU, were made with the 68020. They were very fast for the time. No further PLC’s were developed after the last 68020 boards since TI sold off the industrial systems to Siemens. Thus Siemens obtained the TI customer list and ran with it and Industrial Systems division was closed and all manufacturing in Johnson City, TN was ceased.

April 1st, 2018 at 1:02 am

SOrry, Correction The PM550 used the TMS9900. It was the 555 that used the 68000.

May 31st, 2018 at 12:44 am

Re: James Louie’s comment:

The TMS9900 was ahead of the 8080 and 6502 in some ways, but too expensive for its time. The workspace pointer concept kept it from scaling up in performance as quickly as other processors due to the inherent memory-memory architecture it required, and it had limited address reach. Many years later, the processor architect for the TMS9995 (Karl Guttag) pointed out to me that whatever context switch benefits the WP offered were quickly outweighed by the required memory access cycles only a handful of instructions into an interrupt service routine. It was a false economy.

As crappy as 8086’s segmented approach was, it broke the 64K barrier in a big way while still keeping most pointers 16-bit. In fact, address reach kept the TMS9900 out of the IBM PC. (It was in briefly in the running, alongside the 68K and 8086.)

The TMS9900 family didn’t have a credible path to larger address reach. It tried various external memory mapper shenanigans, but that was more of a hack.

It didn’t help that TI was not great at supporting their processor products at the time. Some of the stories I heard about TI’s design processes at the time also didn’t paint a pretty picture. (I heard of cases where they had taped out chips w/ known power-ground short problems, because tape-outs represented “progress” and management demanded evidence of “progress.”)

Wally Rhines gives an excellent, if brief, retrospective here: https://spectrum.ieee.org/tech-history/heroic-failures/the-inside-story-of-texas-instruments-biggest-blunder-the-tms9900-microprocessor