MIPS CPUS

"Microprocessor without Interlocked

Pipeline Stages"

MIPS Computer Systems is founded, and begins developing

its RISC architecture 1984

Silicon Graphics announces it is acquiring MIPS Computer Systems March

1992

Over the past 20 years, the MIPS® architecture has

continually evolved, but the standard definition of the architecture

has remained simple, streamlined and highly scalable. The initial processors

we developed based on the architecture excelled in a wide range of high-performance

applications, from supercomputers to embedded controllers, beginning

with the 8 MHz, 32-bit R2000 processor, based on the MIPS I™ architecture.

Subsequent processors included the R3000®, the 64-bit R4000™,

and the R5000®, R10000® and R12000®, many of which were

developed while MIPS Technologies was part of Silicon Graphics, Inc.

(SGI).

Feature Table of Past MIPS CPUs

| Feature |

R2000 |

R3000 |

R4000 |

R4200 |

R4300 |

R4400 |

R4600 |

R5000 |

R5200 |

R6000 |

R8000 |

R10000 |

R12000 |

| Introduction |

1985 |

1988 |

1992 |

1993 |

1995 |

1993 |

1994 |

1996 |

199? |

1990 |

1994 |

1995 |

1998 |

| MIPS |

I |

I |

III |

III |

III |

III |

II |

IV |

IV |

II |

IV |

IV |

IV |

| Transistors |

0.11 |

0.11 |

3.7 |

2.3 |

4.6 |

2.3 |

1.9 |

3.7 |

|

|

3.5 |

6.8 |

7.15 |

| Technology |

2u |

1.2u |

.35u |

.6u |

.35u |

.35u |

.35u |

.32u |

|

|

.5u |

..35 |

.25u |

| Register Size |

32 |

32 |

64 |

64 |

64 |

64 |

64 |

64 |

64 |

32 |

64 |

64 |

64 |

| FPU |

2010 |

3010 |

Y |

Y |

Y |

Y |

Y |

Y |

Y |

Y |

Y |

Y |

Y |

| L1 Cache |

128k** |

64k |

16k |

16k+8K |

16k |

32k |

32k |

64k |

64k |

** |

32k |

64k |

64k |

| L2 Cache |

0k |

1M* |

1M* |

128k-4M* |

128k-4M* |

128k-4M* |

128k-4M* |

512K-2M* |

1M |

NA |

|

|

|

| Die size |

80 |

40 |

84 |

90 |

90 |

100 |

70 |

84 |

|

|

289 |

350 |

229 |

| Speeds |

12-33 |

20-40 |

50-250 |

40, 80 |

95,100 |

50-250 |

100-150 |

150-266 |

250, 300 |

60-66 |

75-250 |

180-360 |

270-400 |

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

NOTES:

*Off Chip L2

**Off Chip L1

All values in this table are given by relelease or 'common specs. since

the MIPS is a liscensed design, the parameters such as die size, technology,

and speed will very greatly with the different manufactures and the

different time they were made. many of these cores have been used in

embedded apps with different voltages as well. The graph should however,

give you a general idea of the differences inherent in each class of

the R-Series.

R2000

|

The first commercial MIPS CPU model, the R2000,

was announced in 1985 as a 32-bit implementation. It was used in

the DECstation 2100 and DECstation 3100 as well as several others. |

Back to top

R3000

The R3000 was used in high-end UNIX computers by Siemens and DEC

and in the Silicon Graphics SGI Personal IRIS 4D/20 graphic workstations.

On these machines 3D sequences for movies like The Abyss, Jurrasic

Park or Terminator 2 were rendered. The R3000 was the first really

successful MIPS CPU with over 1 million units produced. The R3000

core was also used in the Sony PSX.

The R3010 is the FPU for the R3000. |

|

Pictures: |

NEC

D30311R-40 VR3010 FPU |

Back to top

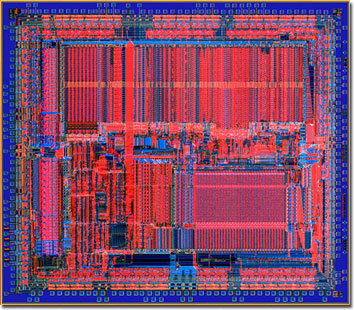

R4000

|

As all R4x00 series processors the R4000 is

a 64bit processor and implements the MIPS III instruction set

thus making the processor compatible to its predecessors. They

contain 32 64bit integer registers and 32 64bit floating point

registers, are superpiplined (8 stages) and approach an execution

rate of one instruction per cycle. contains an onboard MMU with

a TLB (to provide rapid virtual to physical address translation)

and an on-chip R4010 floating point unit. The R4000 contains an

8KB instruction and 8KB data cache for a total of 16KB of on-chip

1st level cache.

The R4x00 processors have been available and used

in different versions. PC (as in "R4000PC") denotes

primary cache only and SC denotes secondary cache. The MC versions

contain special support for cache architectures in multiprocessor

systems. The variants used in SGI systems include SC and PC versions

of the CPU only.

Similar to Sun Microsystems, MIPS designs chips,

but does not manufacture them. Instead, MIPS licensed or sub-contracted

their R4000 line of wafers to custom semiconductor manufacturers

including NEC, Toshiba, LSI Logic, and Integrated Device Technologies

(IDT). Although not apparent from the numerical identification,

the R4000 was preceded by the R6000 processor, which was released

in 1991.

The printed clock speed on early R4000 and R4400

processors is not the cpu clock speed, but the external clock

speed, the internal speed is twice that value. Almost every website

displays the wrong value for clock speed. So the NEC D30401RJ-50

VR4000SC-50 is actually a 100MHz chip. This was changed with the

higher multiplier versions of the R4x00 (50MHz ext. / 200MHz int.

/ multiplier 4.0), this chips are marked with their internal clock

speed.

|

Back to top

R4200

MIPS Technologies announces the R4200 processor. It is designed

to run Windows NT at twice the speed of an Intel 486 processor

Promising "Pentium performance in a notebook," Mips Technologies

announced the first power-saving chip in its R4000

microprocessor family, an important step toward moving RISC chips

from workstations to mainstream PCs. The R4200 was intended primarily

for laptops that can run Windows NT. MIPS said the R4200 could be

powered down and reactivated so quickly that a system could force

the chip into power-down mode between keystrokes when you're typing.

. |

|

Back to top

The R4300, introduced in 1995 by NEC, is a low-cost

but very powerful processor with its external bus reduced to 32 bits.

It was used in the Nintendo64 game console, the NeoGeo Hyper 64 arcade

machine system and many other devices like set-top boxes, video entertainment

systems, arcade games, x-terminals, network hardware and laser printers.

Back to top

R4400

|

As all R4x00 series processors the R4400 is a

64bit processor and implements the MIPS III instruction set thus

making the processor compatible to its predecessors. They contain

32 64bit integer registers and 32 64bit floating point registers,

are superpiplined (8 stages) and approach an execution rate of

one instruction per cycle. It also contains an onbaord MMU with

a TLB (to provide rapid virtual to physical address translation)

and contains an on-chip floating point unit. The R4400 processors

contain 16KB of instruction cache and 16KB of data cache for a

total of 32KB of on-chip 1st level cache. The R4400 processor

can support up to 4MB of off-chip secondary level 2 cache and

all of the 1st level and 2nd level cache control logic resides

on-chip.

Like the R4000 the R4400 CPU is also available with

and without second level cache which is again denoted by the "SC"

and "PC" suffixes. |

Pictures: |

Toshiba

TC86R4400MC-75 |

Back to top

R4600

As all R4x00 series processors the R4600 is a

64bit processor and implements the MIPS III instruction set. The

R4600s are compatible with the R2000, R3000, and R6000 processors.

They contain 32 64bit integer registers and 32 64bit floating

point registers, are superpiplined and approach an execution rate

of one instruction per cycle. It also contains an onbaord MMU

with a TLB (to provide rapid virtual to physical address translation),

and contain an on-chip floating point unit.

Again the PC suffix denotes primary cache only while

the SC suffix denotes that the processor also supports secondary

cache. Both versions were used in SGI workstations - the PC variant

for cheaper entry level systems.

This was designed by QD and is also used in set-top

boxes such as the WebTV |

|

Pictures: |

IDT

79R4600-100

IDT

79R4600-100 - Orion

|

Back to top

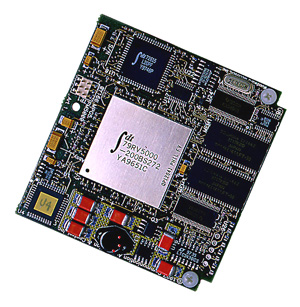

R5000

|

As a lot of R4x00 processors the R5000 has been

available and used in two different versions. The PC version contains

only primary cache and no level 2 cache, while the SC versions

are used with 512 KB secondary cache. The implemented instruction

set is MIPS IV providing also compatibility to the previous instruction

sets. All R5000 processors contain 32 64bit integer registers

and 32 64bit floating point registers. It has a 32KB instruction

cache and a 32KB data cache for a total of 64KB on-chip 1st level

cache.

The R5000 is a 2-issue superscalar microprocessor

which has two execution units that can operate simultaneously,

one for integer operations and one for floating point operations.

Even though the R5000 has two execution units, it cannot always

retire two instructions per cycle. The R5000's execution units

are optimized for single-precision multiply-add operations (common

in 3D geometry calculations). Once the five stage pipeline is

primed, the R5000 can issue a single-precision multiply-add every

cycle. The R5000 can also process an integer or load/store instruction

at the same time as a single-precision multiply-add.

the R5000® processor, developed by QED for NEC

and IDT, with funding by SGI. The R5000 processor added workstation

class floating-point to the R4600 and doubled the cache size yet

again. This processor was the basis for a second generation of

designs in both the networking and printing markets. |

Pictures: |

IDT

79RV5000-150 |

Back to top

R5200

| The 64bit R5200 was used in the SGI O2 workstation. The RM5200A

devices extend the Superscalar architecture of the RM5200 family,

enabling the simultaneous execution of one integer and one floating-point

instruction in a single microprocessor clock cycle. Like their predecessors,

the devices are true 64-bit microprocessors with 64-bit data paths,

64-bit ALUs, 32-bit external access on the RM5231A and 64-bit external

access on the RM5261A. The chips include independent 32KB instruction

and 32KB data caches and provide external peripheral and memory

access at bus speeds exceeding 100MHz. Most notably, these capabilities

and features have been maintained while the microprocessor clock

speed has been increased from 250MHz to 400MHz and the power consumption

has been reduced by 70 percent. PMC-Sierra, Inc. is the first MIPS

licensee to fabricate its microprocessor, in mass production, using

Taiwan Semiconductor Manufacturing Company's (TSMC) advanced 0.18m

"LV" process, a process purposefully developed to optimize

and extend the extremes of both performance and power. |

|

Back to top

R6000

Introduced in 1991

The R6000, an ECL implementation of the MIPS architecture which was

produced by Bipolar Integrated Technology. The R6000 microprocessor

introduced the MIPS II instruction set. Its TLB and cache architecture

are different from all other members of the MIPS family. The R6000 did

not deliver the promised performance benefits, and although it saw some

use in Control Data machines, it quickly disappeared from the mainstream

market.

Physically indexed, virtually tagged

This cache policy is implemented by the R6000. It's believed to be the

only processor which ever implemented it. Some literature calls this

policy outright useless but nevertheless something must have appealed

the R6000 designers enough to go for it. Just to makes things even a

little more interesting the R6000 cache and TLB implementations are

closely related again in a unique way.

Back to top

R8000

|

The first superscalar implementation of the MIPS architecture

is the R8000 (code name "TFP") that has been introduced

in July 1994. The R8000 is a 64bit RISC microprocessor with strong

emphasis on floating point performance, that is spcifically designed

for supercomputing applications. It implements the MIPS IV instruction

set architecture (ISA). One of the remarkable aspects of this processor

is that it is implemented using multiple chips. It's architecture

makes it a processor that is difficult to develop for, so it was

used only for a short period of time and in a limited range of systems.

|

Back to top

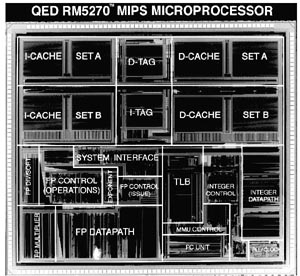

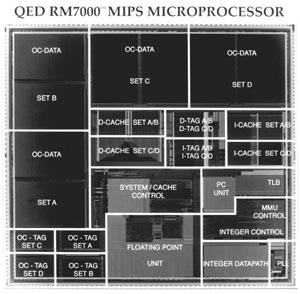

RM7000

PMC-Sierra purchased QED and now makes the RM7000. The the RM7000

(and later products) emphasize on board L2 cache which is very

beneficial to embedded systems.

The newly expanded RM7000 family features the industry leading

RM7000A, RM7000B and RM7065A MIPS CPUs. PMC-Sierra is the only

remaining MIPS RISC vendor to manufacture L2 cache enabled microprocessors

for LAN and WAN internetworking applications. All RM7000 family

CPUs implement true superscalar 64-bit architectures and enable

the simultaneous execution of two integer instructions or one

integer with one floating-point instruction. The processors are

equipped with 64-bit data paths, dual 64-bit ALUs, 64-bit FPUs

and 64-bit system interfaces via the multiplexed address and data

system bus (SysAD). CPU performance ranges from 250 MHz to 500

MHz, with SysAD capability up to 125 MHz. Power dissipation for

this caliber of processor remains an industry benchmark, typically

less than 3.5 W at 400 MHz. All processors are equipped with 256

KB of integrated L2 cache, as well as 16 KB each for independent

L1 instruction and data caches. The RM7000A and RM7000B additionally

contain an L3 cache controller for access of up to 8 MB of external

cache. |

|

Pictures: |

QED

RM7000-250S

QED

RM7000-266T |

Back to top

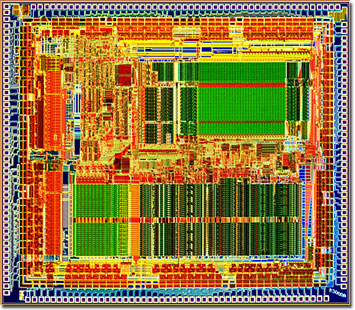

R10000

|

The R10000 'T5' is the first single-chip 4-issue superscalar processor

by MIPS, introduced in 1995. It gave a 70 to 100% performance increase

over the R4400 at 250 MHz, previously the most powerful MIPS processor.

The R10000 CPU was used in NEC supercomputers and various SGI machines

like the Indigo2, O2, Octane, Octane 2, Onyx, Onyx 2, Origin and

Challenge |

Pictures: |

NEC

D30700LRS-225 VR10000

Toshiba

TC86R10000-195 |

Back to top

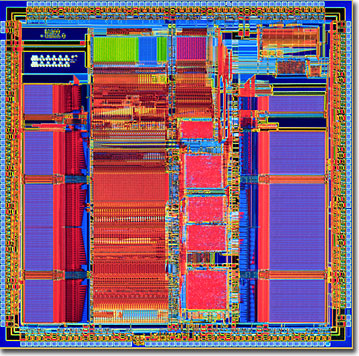

R12000

NEC Corporation (NEC) announced the VR12000-300

microprocessor (part number PD30710RS-300), with performance that

placed it in the highest class of microprocessors in the world.

The VR12000-300 was intended for use by major equipment manufacturers

such as Silicon Graphics, Siemens Nixdorf, and Tandem Computers

as well as by NEC itself. The VR12000-300 microprocessor operates

at 300MHz using a 64-bit RISC design, which simplifies its instruction

sets to accelerate performance. Developed jointly with Silicon

Graphics, Inc., the new microprocessor is compatible with the

MIPS IV instruction set architecture. T

It was used in NEC supercomputers and several SGI

machines like the O2, Octane 2, Onyx 2 and later Origin. |

|

Pictures: |

NEC

D30710RS-275 VR12000 |

Back to top

If you have any more info on R-series MIPS CPUs please

let me know

|