Zycad: Emulating Hardware on Hardware

Zycad was founded in 1981 to develop and market simulation acceleration technology. This was to allow new chip designs to be tested/simulated before being laid out in silicon, providing the possibility to catch faults earlier in the design process. The earlier faults can be caught, the easier, and less expensive they are to fix.

By the late 1980’s Zycad a leader in simulation tech and set the standard for simulation systems. They provided the simulation software environment, a simulation/hardware descriptive language (Zycad Intermediate Format), as well as custom hardware accelerators for the logic/fault simulation.

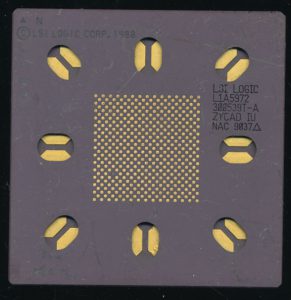

In 1987 Zycad shipped a customized system to LSI, which LSI was then able to use, and market for all their customer designs, notable the LSI version of the SPARC processor. This close relationship with LSI also benefited Zycad, as it was LSI who fab’d Zycad’s custom silicon, the heart of their emulation system. In the late 80’s and early 90’s the main Zycad emulation system was the XP series. The XP series (consisting of the 100, 140 and 200) was based on 2 main IC’s. The Interface Control Processor (IU) was the interface between the host processor (either a SPARC system, or a VAX type workstation) and the Logic/Fault Emulation Processors (PU’s). One IU could control multiple PU’s and a typical system (such as the XP-140) had 1 IU and 5 PU’s. These systems could emulate from 256,000 (XP-100) to 4 million (XP-200) gates at speeds from 2.5 millions events/sec to 40 million events/sec.

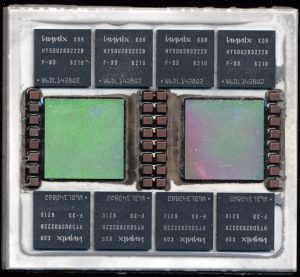

In 1996 Zycad announced the Lightspeed simulation server, massively parallel simulation server running on from 64-4096 processors, each with their own on chip memory. These were implemented on 0.5u ASICs from LSI. This technology was sold later that year to one of Zycad’s competitors, IKOS, leaving Zycad to enter the field of FPGAs as Gatefield, which later would be bought out by Actel. IKOS was later acquired by Mentor Graphics, a company that worked extensively with Zycad and their emulators in the 1980’s and 1990’s. The customer, had now become the owner.

What Zycad began in the 1980’s continues today on a massive scale. The XP series and the later Lightspeed simulation server are in many ways similar to the Palladium and Palladium II processors by Quickturn/Cadence that we discussed lat year.

Hardware simulation is a field that continues to grow in scale and complexity. As systems become more and more complex, transistors counts continue to rise, and the need to make sure it works, before putting it in silicon remains.

Posted in:

CPU of the Day