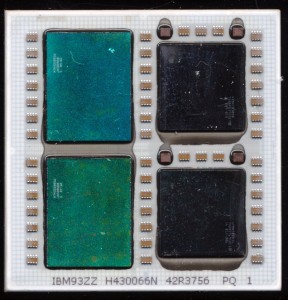

CPU of the Day: IBM POWER5+ QCM

When the POWER5 processor was released in 2004 it was made in two versions, a DCM (Dual Chip Module) containing a POWER5 die and its 36MB L3 cache die, as well as a MCM containing 4 POWER5 die and 4 L3 cache dies totaling 144MB. The POWER5 is a dual core processor, thus the DCM was a dual core, and the MCM an 8 core processor. The POWER5 contains 276 million transistors and was made on a 130nm CMOS9S process.

In 2005 IBM shrank the POWER5 onto a 90nm CMOS10S manufacturing process resulting in the POWER5+. This allowed speeds to increase to 2.3GHz from the previous max of 1.9GHz. The main benefit from the process shrink was less power draw, and thus less heat. This allowed IBM to make the POWER5+ in a QCM (Quad Chip Module) as well as the previous form factors. The QCM ran at up to 1.8GHz and contained a pair of POWER5+ dies and 72MB of L3 Cache.

The POWER5+ was more then a die shrink, IBM reworked much of the POWER5 to improve performance, adding new floating point instructions, doubling the TLB size, improved SMP support, and an enhanced memory controller to mention just a few.

The result? A much improved processor and a very fine looking QCM.

March 2nd, 2014 at 7:52 am

“The POWER5 is a dual core processor, thus the DCM was a quad core, and the MCM an 8 core processor.”

As stated, the Dual Chip Module contained *one* processor chip and an L3 cache chip, so it was only a dual core.

March 6th, 2014 at 3:01 pm

Right you are, thanks for pointing out my oops.

December 22nd, 2017 at 11:29 am

Thanks, it was very helpful! I’ve just acquired a DCM, probably the one you mentioned because it looks pretty much half of the QCM on the photo. The two dies seem to have the same sizes and the module markings are IBM93ZZ G240230F 40N1853 PQ 1.

Is there any guide that helps me decipher these codes?

December 22nd, 2017 at 11:36 am

Probably a POWER5+ DCM then (or if one of the dies is a bit bigger then an original POWER 5 DCM). THere isnt a guide unfortunately as IBM part #s are very hard to work out (and there is a lot of them for each part). I have been working on one for POWER6/7/8 though